## **POWER ELECTRONICS**

**Devices, Drivers, Applications, and Passive Components**

Barry W Williams

B.Sc., Dipl.Eng., B.Eng., M.Sc., Ph.D., D.I.C.

Professor of Electrical Engineering

University of Strathclyde, Glasgow

Power Electronics ii

#### **Table of Contents**

#### 1

#### **Basic Semiconductor Physics and Technology**

|    |         | -                                               |   |

|----|---------|-------------------------------------------------|---|

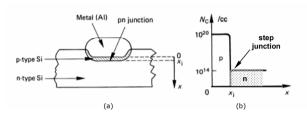

| .1 | Proces  | sses forming pn junctions                       | 2 |

|    | 1.1.1   | The alloyed junction                            |   |

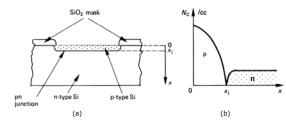

|    | 1.1.2   | The diffused junction                           |   |

|    | 1.1.3   | The epitaxy junction                            |   |

|    | 1.1.4   | The ion-implanted junction                      |   |

|    | 1.1.5   | The ohmic-contact junction                      |   |

| .2 | The ox  | cidation and masking process                    | 5 |

| .3 | Polysil | licon deposition                                | 5 |

| .4 | Lifetin | ne control                                      | 5 |

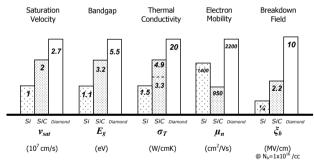

| .5 | Silicon | ı Carbide                                       | 6 |

| .6 | Si and  | SiC physical and electrical properties compared | 7 |

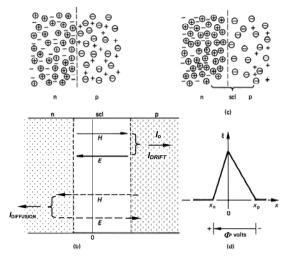

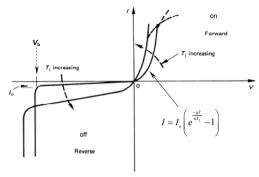

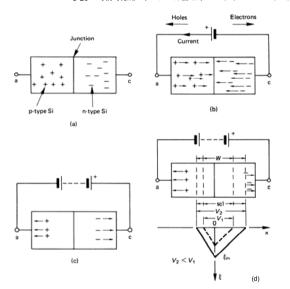

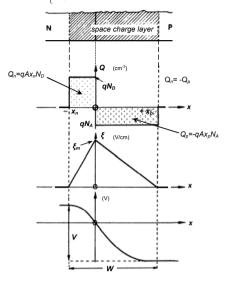

| The | e pn Ju                                   | ınction                                                                                                                                                                                                                                  |                            |               |

|-----|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------|

| 2.1 | The p                                     | n junction under forward bias (steady-state                                                                                                                                                                                              | )                          | 10            |

| 2.2 | The p                                     | n junction under reverse bias (steady-state)                                                                                                                                                                                             |                            | 10            |

|     | 2.2.1<br>2.2.2<br>2.2.3                   | Punch-through voltage<br>Avalanche breakdown<br>Zener breakdown                                                                                                                                                                          |                            |               |

| 2.3 | Thern                                     | nal effects                                                                                                                                                                                                                              |                            | 13            |

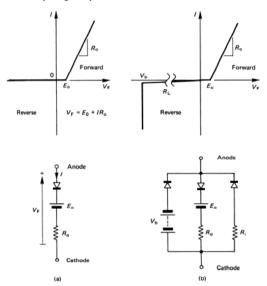

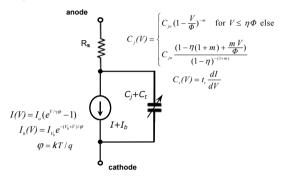

| 2.4 | Model                                     | s for the junction diode                                                                                                                                                                                                                 |                            | 14            |

| 2   |                                           | ole 2.1: Using the pwl junction diode mode le 2.2: Static diode mode!  Semiconductor physics based junction diode 2.4.2i - Determination of C <sub>jo</sub> 2.4.2ii - One-sided pn diode equal ole 2.3: Space charge layer parameter val | de mode                    | e <b>l</b> 18 |

|     |                                           | vitching Devices<br>Static Electrical Character                                                                                                                                                                                          | ristic                     | es            |

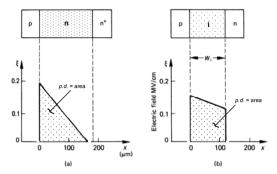

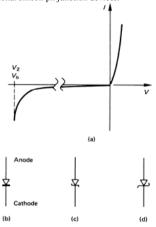

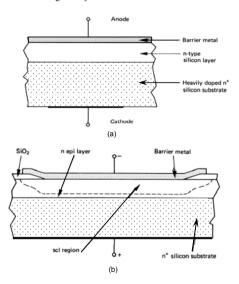

| 3.1 | Power                                     | diodes                                                                                                                                                                                                                                   |                            | 25            |

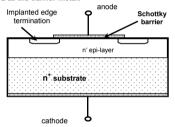

|     | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5 | The pn fast-recovery diode<br>The p-i-n diode<br>The power Zener diode<br>The Schottky barrier diode<br>The silicon carbide Schottky barrier diode                                                                                       | 25<br>27<br>28<br>29<br>32 |               |

| 3.2 | Power                                     | switching transistors                                                                                                                                                                                                                    |                            | 32            |

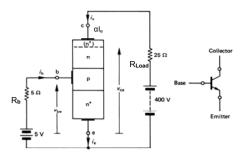

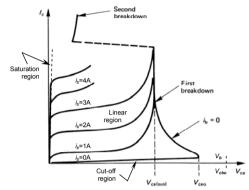

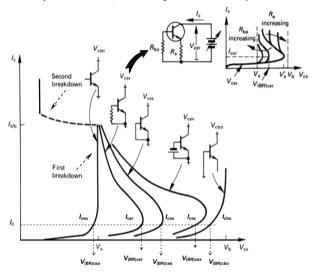

3.2.1 The bipolar npn power switching transistor (BJT) 33

3.2.1iii - BJT maximum voltage - first and second breakdown

3.2.1i - BJT gain

3.2.1ii - BJT operating states

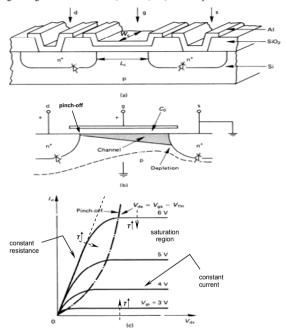

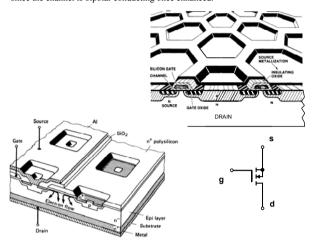

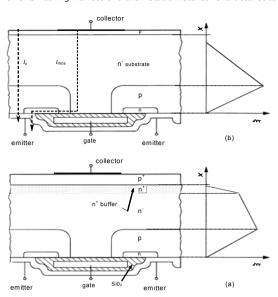

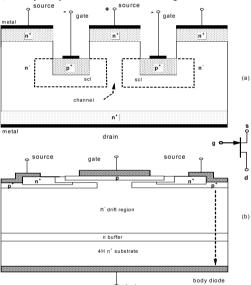

|     | 3.2.2 | The metal oxide semiconductor field effec   | t transistor (MOSFET)37 |

|-----|-------|---------------------------------------------|-------------------------|

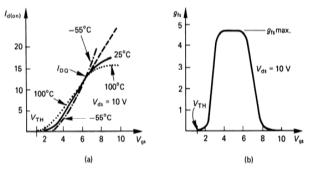

|     |       | 3.2.2i - MOSFET structure and characteris   | stics                   |

|     |       | 3.2.2ii - MOSFET drain current              |                         |

|     |       | 3.2.2iii -MOSFET transconductance           |                         |

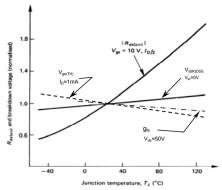

|     |       | 3.2.2iv - MOSFET on-state resistance        |                         |

|     |       | 3.2.2v - MOSFET p-channel device            |                         |

|     | Examp | ple 3.1: Properties of an n-channel MO      | SFET cell               |

|     |       | 3.2.2vi - MOSFET parasitic BJT              |                         |

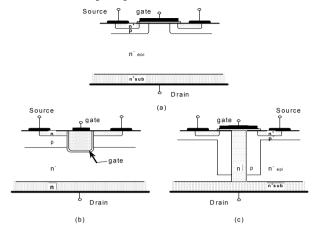

|     |       | 3.2.2vii - MOSFET on-state resistance reduc | tion                    |

|     |       | 1 - trench gate                             |                         |

|     |       | 2 - vertical super-junction                 |                         |

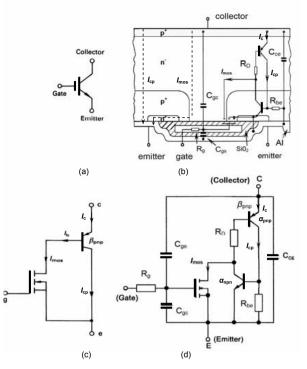

|     | 3.2.3 | The insulated gate bipolar transistor (IG   | BT) 46                  |

|     |       | 3.2.3i - IGBT at turn-on                    |                         |

|     |       | 3.2.3ii - IGBT in the on-state              |                         |

|     |       | 3.2.3iii - IGBT at turn-off                 |                         |

|     |       | 3.2.3iv - IGBT latch-up                     |                         |

|     |       | 1 - IGBT on-state SCR static latch-         | ир                      |

|     |       | 2 - IGBT turn-off SCR dynamic la            | tch-up                  |

|     | 3.2.4 | The junction field effect transistor (JFET  | r) 50                   |

|     |       | PT IGBT and NPT IGBT comparison             | 50                      |

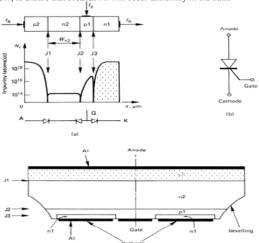

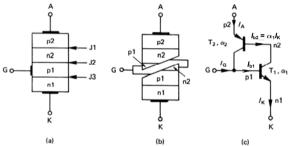

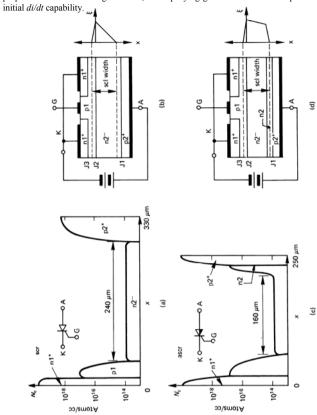

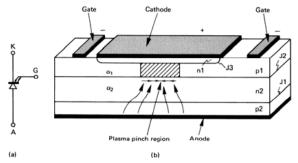

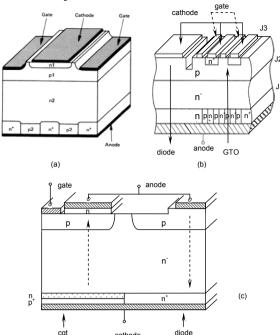

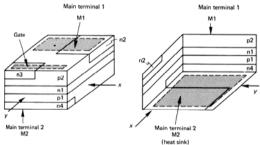

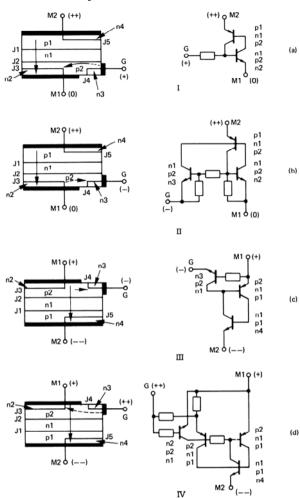

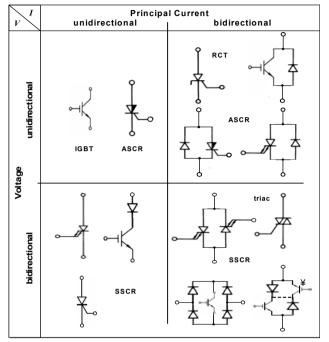

| 3.3 | Thyr  | istors                                      | 51                      |

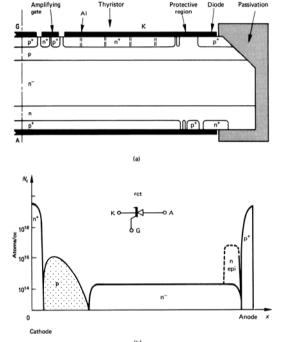

|     | 3.3.1 | The silicon-controlled rectifier (SCR)      | 51                      |

|     | 0.011 | 3.3.1i - SCR turn-on                        |                         |

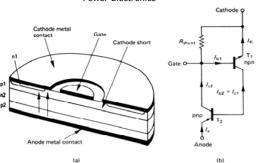

|     |       | 3.3.1ii - SCR cathode shorts                |                         |

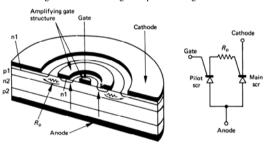

|     |       | 3.3.1iii - SCR amplifying gate              |                         |

|     | 3.3.2 |                                             | tifier (ASCR)57         |

|     | 3.3.3 |                                             | 57                      |

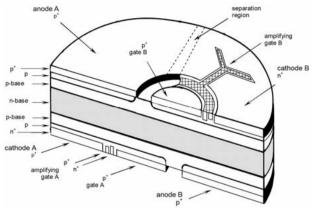

|     | 3.3.4 |                                             | (BCT)60                 |

|     | 3.3.5 | The gate turn-off thyristor (GTO)           | 61                      |

|     |       | 3.3.5i - GTO turn-off mechanism             |                         |

|     | 3.3.6 | The gate commutated thyristor (GCT)         | 62                      |

|     |       | 3.3.6i - CGT turn-off                       |                         |

|     |       | 3.3.6ii - GCT turn-on                       |                         |

|     | 3.3.7 | The light triggered thyristor (LTT)         | 64                      |

|     | 3.3.8 | The triac                                   | 64                      |

|     |       |                                             |                         |

Power Electronics

|   | Power Electronics |  |

|---|-------------------|--|

| • | Power Electronics |  |

| 4 |

|---|

| / |

| 4 |

| <b>Electrical Ratings and Characteristics</b> |

|-----------------------------------------------|

| of Power Semiconductor Switching Devices      |

| 4.1 | Gener  | al maximum ratings of power semiconduc     | tor devi  | ces 68 |

|-----|--------|--------------------------------------------|-----------|--------|

|     | 4.1.1  | Voltage ratings                            | 69        |        |

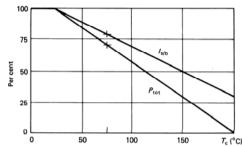

|     | 4.1.2  |                                            | 71        |        |

|     | 4.1.3  | Temperature ratings                        | 71        |        |

|     | 4.1.4  | Power ratings                              | 71        |        |

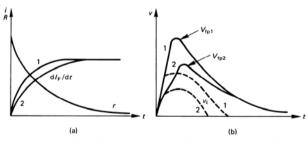

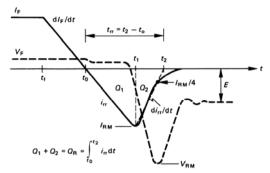

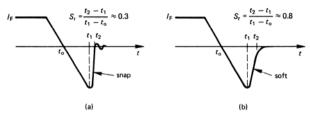

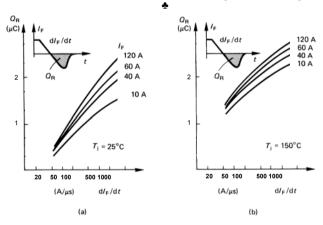

| 4.2 | The fa | st-recovery diode                          |           | 71     |

|     | 4.2.1  | Turn-on characteristics                    | 72        |        |

|     | 4.2.2  | Turn-off characteristics                   | 73        |        |

|     | 4.2.3  | Schottky diode dynamic characteristics     | 75        |        |

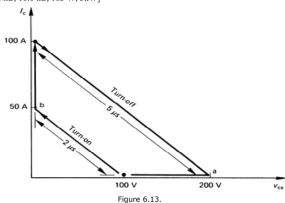

| 4.3 | The bi | polar, high-voltage, power switching npn   | transiste | or 75  |

|     | 4.3.1  | Transistor ratings                         | 76        |        |

|     |        | 4.3.1i - BJT collector voltage ratings     |           |        |

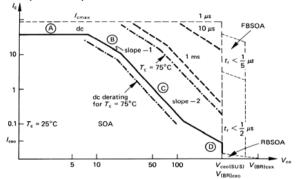

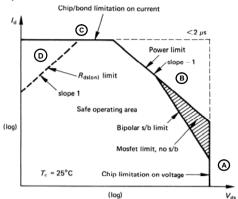

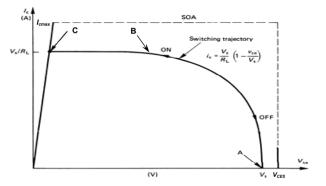

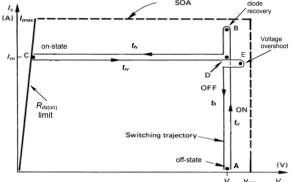

|     |        | 4.3.1ii – BJT safe operating area (SOA)    |           |        |

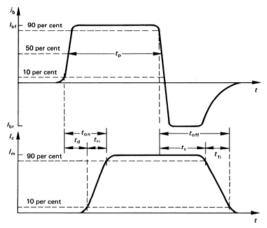

|     | 4.3.2  | Transistor switching characteristics       | 80        |        |

|     |        | 4.3.2i – BJT turn-on time                  |           |        |

|     |        | 4.3.2ii – BJT turn-off time                |           |        |

|     | 4.3.3  | BJT phenomena                              | 82        |        |

| 4.4 | The pe | ower MOSFET                                |           | 83     |

|     | 4.4.1  | MOSFET absolute maximum ratings            | 83        |        |

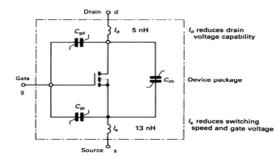

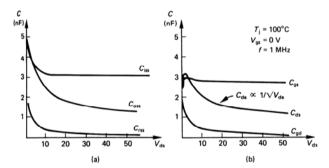

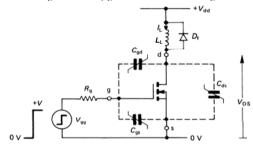

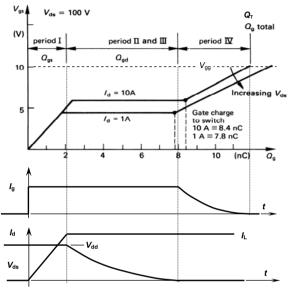

|     | 4.4.2  | Dynamic characteristics                    | 84        |        |

|     |        | 4.4.2i - MOSFET device capacitances        |           |        |

|     |        | 4.4.2ii – MOSFET switching characteristics |           |        |

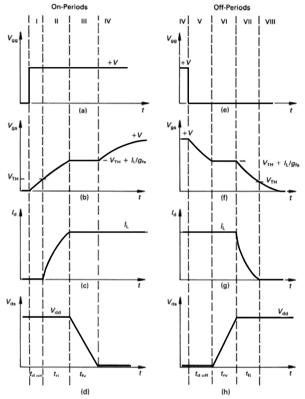

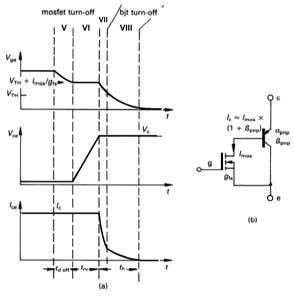

|     |        | 1 - MOSFET turn-on                         |           |        |

|     |        | 2 - MOSFET turn-off                        |           |        |

| 4.5 | The in | sulated gate bipolar transistor            |           | 90     |

|     | 4.5.   | IGBT switching                             | 90        |        |

|     | 4.5.2  | IGBT short circuit operation               | 92        |        |

|     |        | 1021 short en enn operation                |           |        |

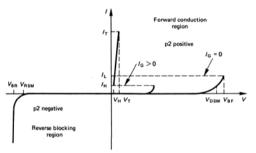

| 4.6 | The th | yristor                                    |           | 93     |

|     | 4.6.1  | SCR ratings                                | 93        |        |

|     |        | 4.6.1i - SCR anode ratings                 |           |        |

| Power Electronics | vi |

|-------------------|----|

|                   |    |

|     |                  | 4.6.1ii - SCR gate ratings                                                                                                                                                           |            |          |

|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|

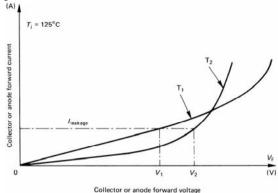

|     | 4.6.2            | Static characteristics                                                                                                                                                               | 95         |          |

|     |                  | 4.6.2i - SCR gate trigger requirements                                                                                                                                               |            |          |

|     |                  | 4.6.2ii - SCR holding and latching current                                                                                                                                           |            |          |

|     | 4.6.3            | Dynamic characteristics                                                                                                                                                              | 96         |          |

|     |                  | 4.6.3i - SCR anode at turn-on                                                                                                                                                        |            |          |

|     |                  | 4.6.3ii - SCR anode at turn-off                                                                                                                                                      |            |          |

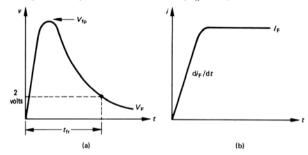

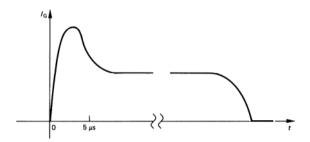

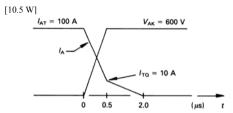

| 4.7 | The ga           | ate turn-off thyristor                                                                                                                                                               |            | 97       |

|     | 4.7.1 7          | Turn-on characteristics                                                                                                                                                              | 97         |          |

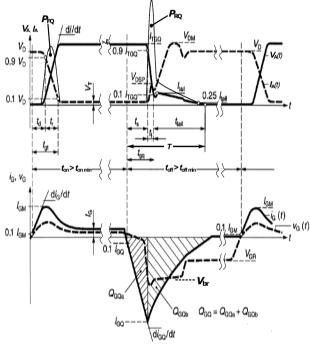

|     | 4.7.2 7          | Furn-off characteristics                                                                                                                                                             | 97         |          |

| 4.8 | Appen            | dix: Effects on MOSFET switching of neg                                                                                                                                              | ative gate | drive 99 |

| 5   |                  |                                                                                                                                                                                      |            | 10       |

|     | oling o<br>vices | of Power Switching Semico                                                                                                                                                            | onduc      | tor      |

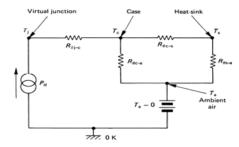

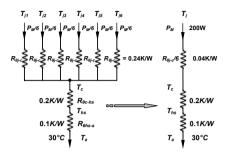

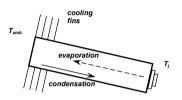

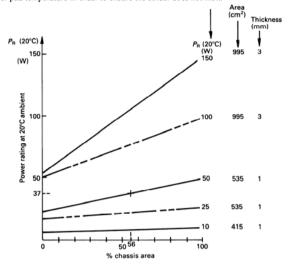

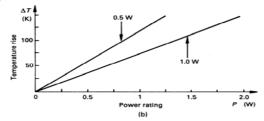

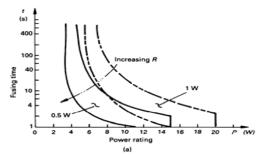

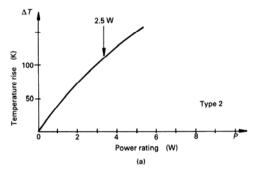

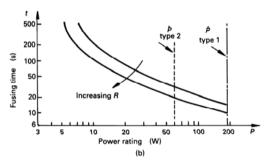

| 5.1 | Thern            | nal resistances                                                                                                                                                                      |            | 101      |

|     | 5.1.1            | Contact thermal resistance, $R_{\theta s-s}$                                                                                                                                         | 101        |          |

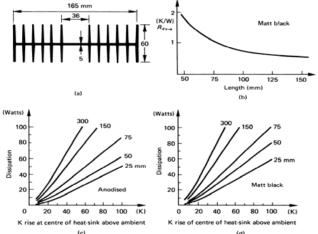

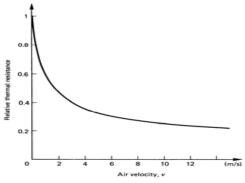

|     | 5.1.2            | Heat-sink thermal resistance, $R_{\theta_{8-a}}$                                                                                                                                     | 102        |          |

| 5.2 | Modes            | s of power dissipation                                                                                                                                                               |            | 105      |

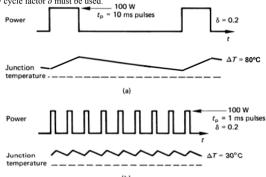

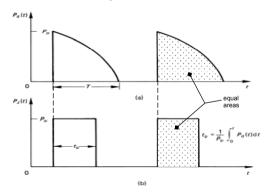

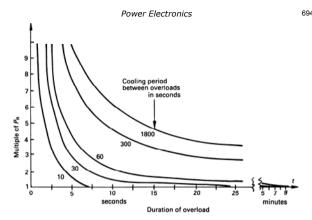

|     | 5.2.1            | Pulse response                                                                                                                                                                       | 107        |          |

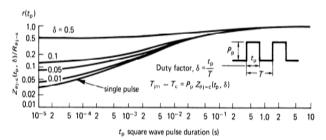

|     | 5.2.2            |                                                                                                                                                                                      | 108        |          |

| 5.3 | Avera            | Steady-state response                                                                                                                                                                |            |          |

|     | 5.3.1            |                                                                                                                                                                                      |            | 109      |

|     | 5.3.2            | Steady-state response                                                                                                                                                                | 109        | 109      |

|     |                  | Steady-state response ge power dissipation                                                                                                                                           | 109<br>109 | 109      |

| 5.4 | Power            | Steady-state response ge power dissipation Graphical integration                                                                                                                     |            | 109      |

| 5.4 | Power 5.4.1      | Steady-state response ge power dissipation Graphical integration Practical superposition                                                                                             |            |          |

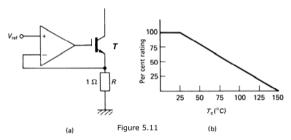

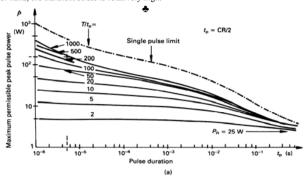

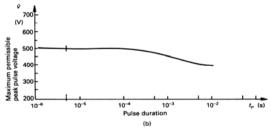

| 5.4 |                  | Steady-state response  ge power dissipation  Graphical integration  Practical superposition  closses from manufacturers' data sheets                                                 | 109        |          |

| 5.4 | 5.4.1            | Steady-state response  ge power dissipation  Graphical integration  Practical superposition  losses from manufacturers' data sheets  Switching transition power loss, P <sub>s</sub> | 109<br>109 |          |

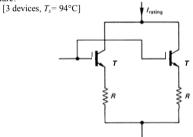

| 5.5  | Heat-sinking design cases        |                                                                                          | 111                    |                |  |

|------|----------------------------------|------------------------------------------------------------------------------------------|------------------------|----------------|--|

|      | 5.5.1                            | Heat-sinking for diodes and thyristors                                                   | 113                    |                |  |

|      |                                  | 5.5.1i - Low-frequency switching                                                         |                        |                |  |

|      |                                  | 5.5.1ii - High-frequency switching                                                       |                        |                |  |

|      | Exampl                           |                                                                                          |                        |                |  |

|      |                                  | Heat-sinking for IGBTs                                                                   | 116                    |                |  |

|      | Exampl                           | e 5.2: Heat-sink design for an IGBT - repetitive operation at a high                     | dutu anala             |                |  |

|      | 5.5.3                            | - repetitive operation at a night<br>Heat-sinking for power MOSFETs                      | l auty cycle<br>117    |                |  |

|      | Example                          | 3, 1                                                                                     | 11/                    |                |  |

|      | Example                          | - repetitive operation at high peak                                                      | current. low           | duty cycle     |  |

|      | Example                          |                                                                                          | rearread, ton          | and eyele      |  |

|      |                                  | - repetitive operation at high a                                                         | lutv cvcle             |                |  |

|      | Example                          | e 5.5: Two thermal elements a common                                                     |                        |                |  |

|      |                                  | e 5.6: Six thermal elements in a commo                                                   |                        |                |  |

|      | •                                |                                                                                          |                        |                |  |

|      |                                  |                                                                                          |                        |                |  |

|      |                                  |                                                                                          |                        |                |  |

| 6    |                                  |                                                                                          |                        |                |  |

| •    |                                  |                                                                                          |                        | 122            |  |

|      | 10.                              | . 10                                                                                     |                        |                |  |

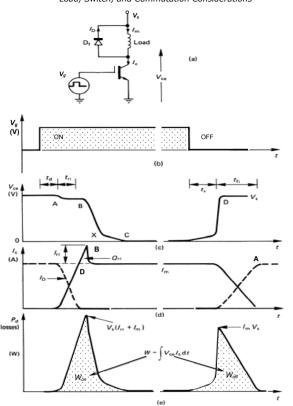

| Load | a, Swi                           | tch, and Commutation C                                                                   | onside                 | rations        |  |

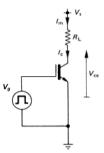

| 6.1  |                                  | Load types                                                                               |                        | 122            |  |

|      |                                  | ••                                                                                       | 122                    |                |  |

|      | 6.1.1                            | The resistive load                                                                       | 123                    |                |  |

|      | Example                          |                                                                                          |                        |                |  |

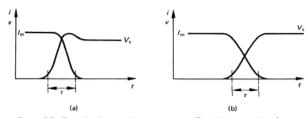

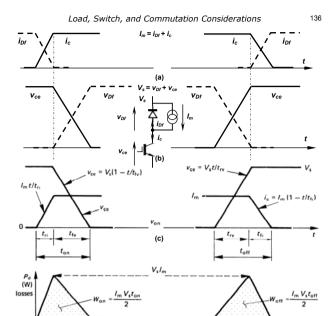

|      | Example 6.1.2                    | e 6.2: Transistor switching loss for non-<br>The inductive load                          | linear electric<br>129 | al transitions |  |

|      | Example                          |                                                                                          |                        |                |  |

|      | Example                          |                                                                                          |                        |                |  |

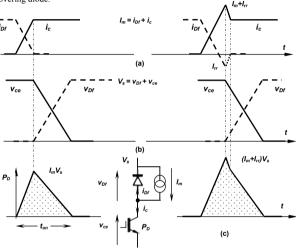

|      | 6.1.3                            | Diode reverse recovery with an inductiv                                                  |                        |                |  |

|      |                                  |                                                                                          |                        |                |  |

| 6.2  | Switch o                         | characteristics                                                                          |                        | 137            |  |

| 6.3  | Cavitabia                        | ng classification                                                                        |                        | 138            |  |

| 0.0  |                                  |                                                                                          |                        |                |  |

|      |                                  |                                                                                          |                        | 100            |  |

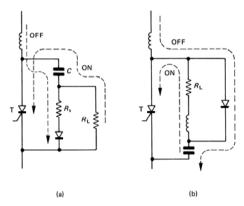

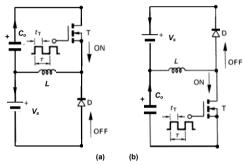

|      | 6.3.1                            | Hard switching                                                                           | 139                    |                |  |

|      | 6.3.1<br>6.3.2                   | Hard switching Soft switching                                                            | 139                    | 100            |  |

|      | 6.3.1<br>6.3.2<br>6.3.3          | Hard switching<br>Soft switching<br>Resonant switching                                   | 139<br>139             |                |  |

|      | 6.3.1<br>6.3.2                   | Hard switching Soft switching                                                            | 139                    |                |  |

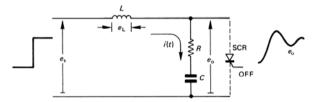

| 6.4  | 6.3.1<br>6.3.2<br>6.3.3<br>6.3.4 | Hard switching<br>Soft switching<br>Resonant switching<br>Naturally-commutated switching | 139<br>139             |                |  |

| 6.4  | 6.3.1<br>6.3.2<br>6.3.3<br>6.3.4 | Hard switching<br>Soft switching<br>Resonant switching                                   | 139<br>139             | 141            |  |

| 6.4  | 6.3.1<br>6.3.2<br>6.3.3<br>6.3.4 | Hard switching<br>Soft switching<br>Resonant switching<br>Naturally-commutated switching | 139<br>139             |                |  |

|     | Power Electronics                                                                                                                                                                                              | viii                                          |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 7   |                                                                                                                                                                                                                |                                               |

| ъ.  |                                                                                                                                                                                                                | 144                                           |

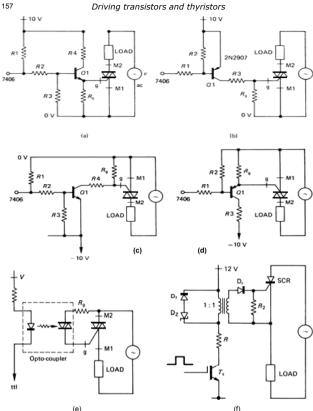

| Drr | ving Transistors and Thyristor                                                                                                                                                                                 | 'S                                            |

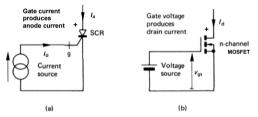

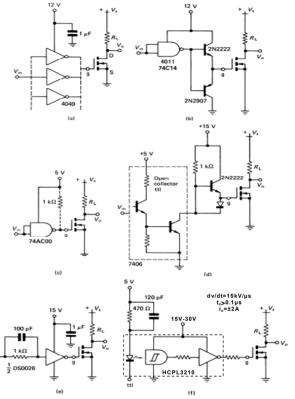

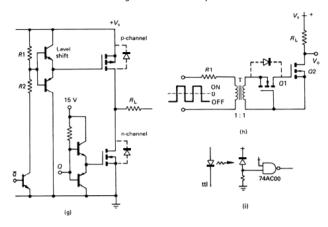

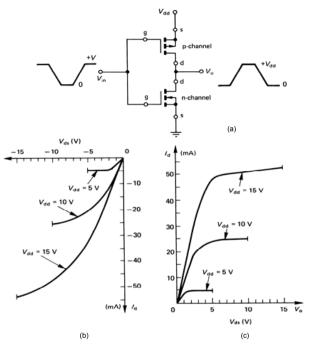

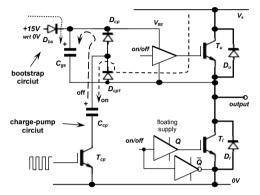

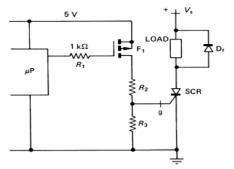

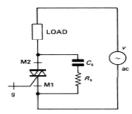

| 7.1 | Application of the power MOSFET and IGBT                                                                                                                                                                       | 145                                           |

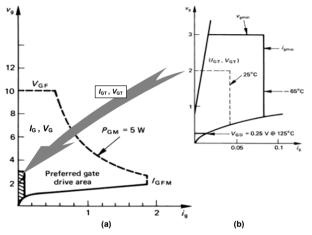

|     | 7.1.1 Gate drive circuits 7.1.1i - Negative gate drive 7.1.1ii - Floating power supplies 1 - capacitive coupled charge pum 2 - diode bootstrap 7.1.2 Gate drive design                                         | p 153                                         |

|     | Example 7.1: MOSFET input capacitance a                                                                                                                                                                        |                                               |

| 7.2 | Application of the Thyristor                                                                                                                                                                                   | 156                                           |

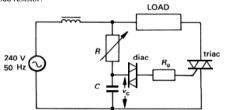

|     | 7.2.1 Thyristor gate drive circuits 7.2.2 Thyristor gate drive design Example 7.2: A light dimmer                                                                                                              | 158<br>158                                    |

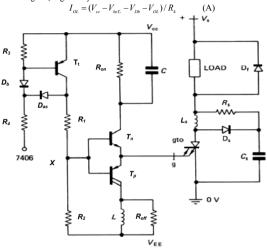

| 7.3 | Drive design for GTO thyristors                                                                                                                                                                                | 161                                           |

| 8   |                                                                                                                                                                                                                |                                               |

| Pro | tecting Diodes, Transistors, an                                                                                                                                                                                | d Thyristors                                  |

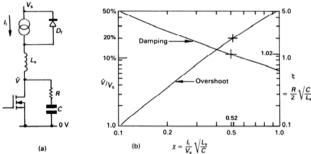

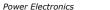

| 8.1 | The R-C snubber                                                                                                                                                                                                | 166                                           |

|     | 8.1.1 R-C switching aid circuit for the MOSI Example 8.1: R-C snubber design for MOSI 8.1.2 R-C snubber circuit for a converter gra Off-state dv/dt suppression snu Example 8.2: R-C snubber design for a conv | FETs<br>ade thyristor and a triac<br>ubber168 |

| 8.2 | The soft voltage clamp                                                                                                                                                                                         | 172                                           |

|     | Example 8.3: Soft voltage clamp design                                                                                                                                                                         |                                               |

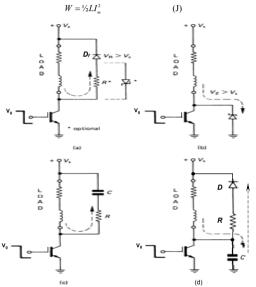

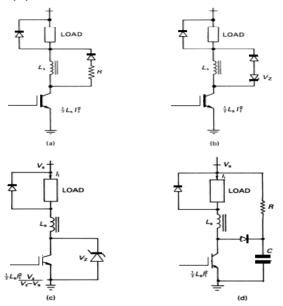

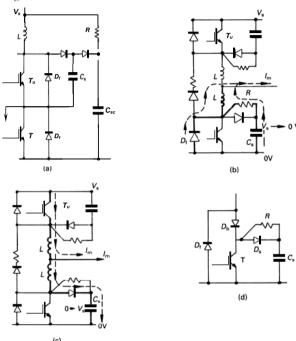

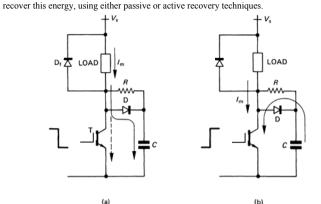

| 8.3 | Switching-aid circuits                                                                                                                                                                                         | 176                                           |

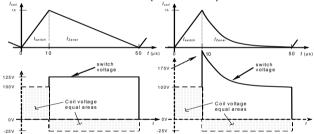

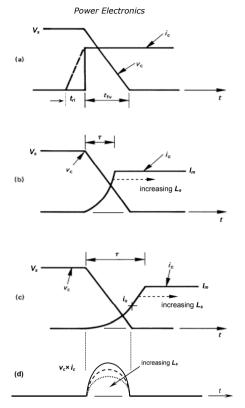

An inductive turn-on snubber

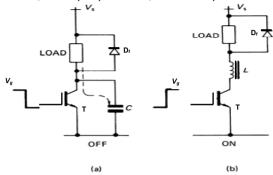

The capacitive turn-off snubber

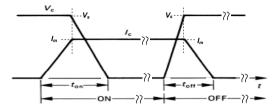

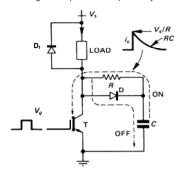

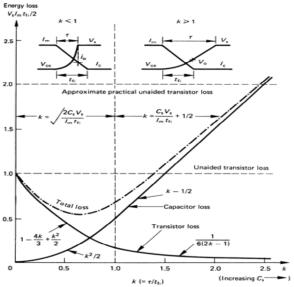

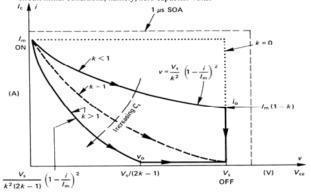

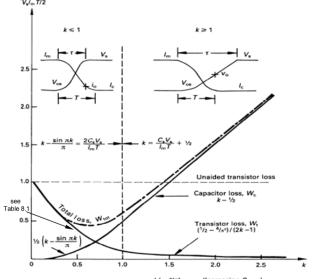

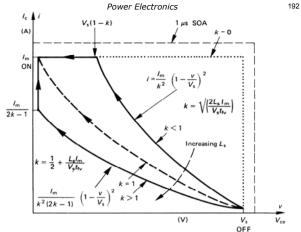

8.3.1 The turn-off snubber circuit

- assuming a linear current fall 178

8.3.2 The turn-off snubber circuit

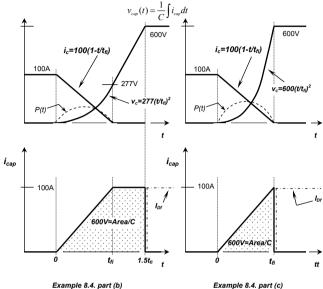

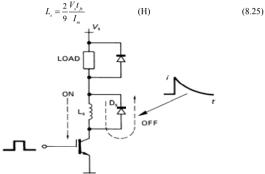

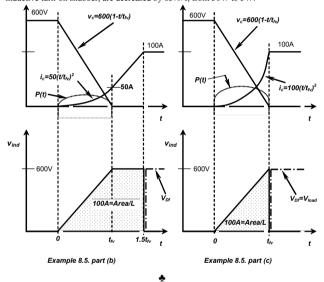

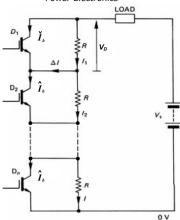

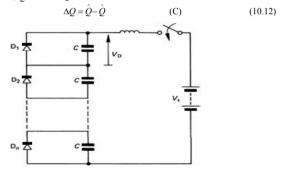

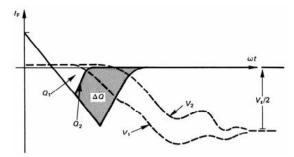

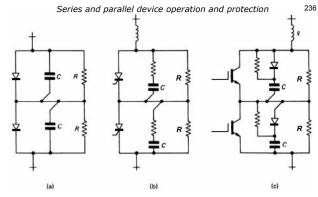

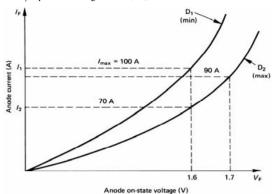

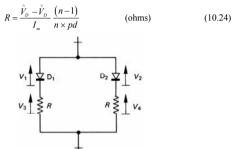

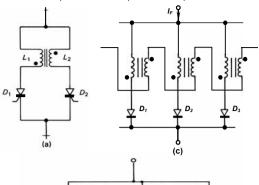

|            | - assuming a cosinusoidal current fall 175  Example 8.4: Turn-off snubber design  8.3.3 The turn-on snubber circuit - with non-saturable (air-core) inductance185  Example 8.5: Turn-on air-core inductor snubber design  8.3.4 The turn-on snubber circuit - with saturable ferrite inductance 188 | Example 10.2: Series device connection – dynamic balan 10.1.2 Parallel operation 236 10.1.2i - Matched devices 10.1.2i - External forced current sharing Example 10.3: Resistive parallel current sharing - static Example 10.4: Transformer current sharing – static and dynam | balancing |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

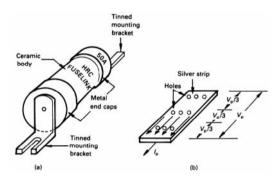

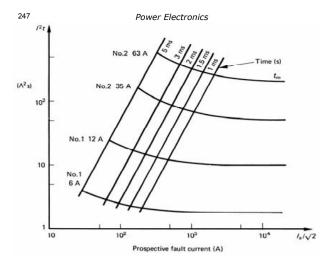

|            | Example 8.6: Turn-on ferrite-core inductor snubber design                                                                                                                                                                                                                                           | 10.2 Protection                                                                                                                                                                                                                                                                 | 242       |

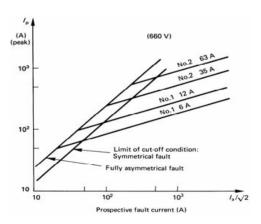

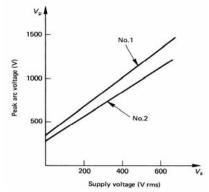

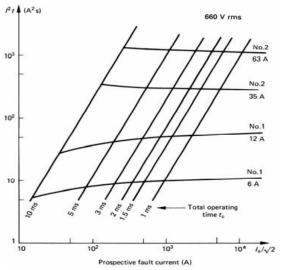

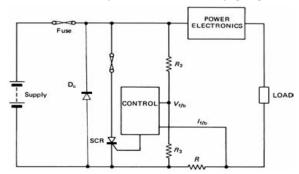

| 8.4<br>8.5 | 8.3.5 The unified snubber circuit Snubbers for bridge legs 201  Appendix: Turn-off R-C snubber circuit analysis 204                                                                                                                                                                                 | 10.2.1 Overcurrent 242<br>10.2.1i - Pre-arcing I <sup>2</sup> t<br>10.2.1ii - Total I <sup>2</sup> t let-through                                                                                                                                                                |           |

| 8.6        | Appendix: Turn-off <i>R-C-D</i> switching aid circuit analysis 205                                                                                                                                                                                                                                  | 10.2.1iii - Fuse link and semiconductor I <sup>2</sup> t co-ordinatic<br>Example 10.5: AC circuit fuse design<br>10.2.2 Overvoltage 251<br>10.2.2i - Transient voltage suppression devices                                                                                      | n         |

| 9          | 21                                                                                                                                                                                                                                                                                                  | 10.2.2ii - Comparison between Zener diodes and varisto.  Example 10.6: Non-linear voltage clamp  10.2.3 Crowbar 257  10.2.4 Noise 258                                                                                                                                           | rs        |

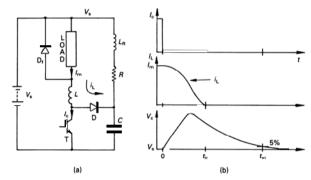

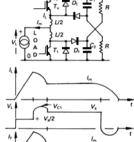

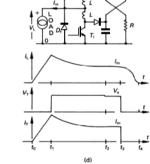

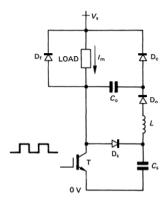

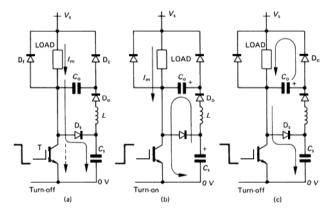

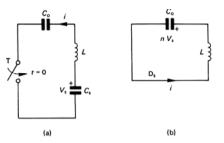

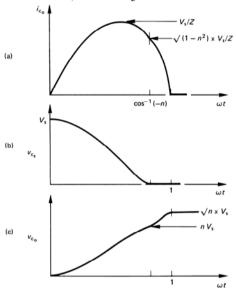

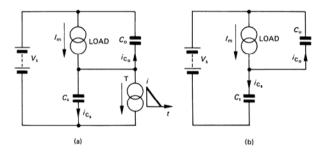

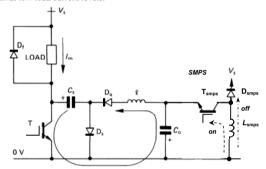

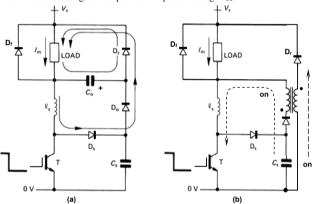

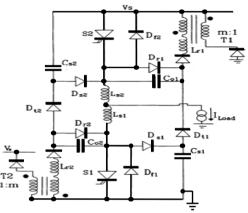

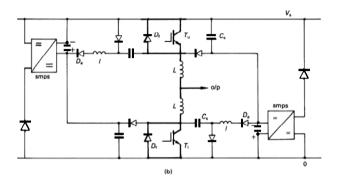

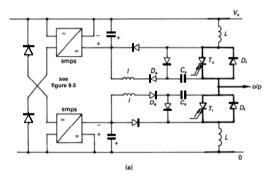

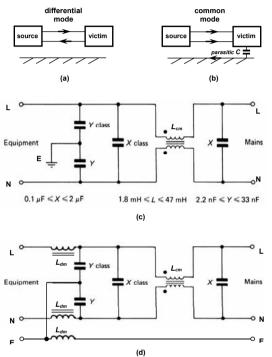

| Swit       | ching-aid Circuits with Energy Recovery                                                                                                                                                                                                                                                             | 10.2.4 Fonducted noise                                                                                                                                                                                                                                                          |           |

| 9.1        | Energy recovery for turn-on snubber circuits 211  9.1.1 Passive recovery 212                                                                                                                                                                                                                        | 10.2.4ii - Radiated electromagnetic field coupling<br>10.2.4iii - Electric field coupling<br>10.2.4iv - Magnetic field coupling                                                                                                                                                 |           |

|            | 9.1.2 Active recovery 214                                                                                                                                                                                                                                                                           | 10.2.5 Mains filters 261<br>10.2.6 Noise filtering precautions 261                                                                                                                                                                                                              |           |

| 9.2        | Energy recovery for turn-off snubber circuits 215                                                                                                                                                                                                                                                   | 11                                                                                                                                                                                                                                                                              |           |

|            | 9.2.1       Passive recovery       216         9.2.2       Active recovery       222                                                                                                                                                                                                                | 11                                                                                                                                                                                                                                                                              | 264       |

| 9.3        | Unified turn-on and turn-off snubber circuit energy recovery 223                                                                                                                                                                                                                                    | Naturally Commutating Converters                                                                                                                                                                                                                                                |           |

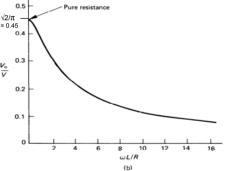

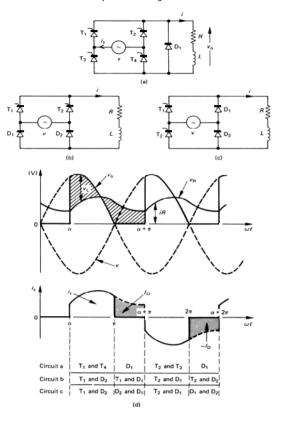

|            | 9.3.1     Passive recovery     223       9.3.2     Active recovery     224                                                                                                                                                                                                                          | 11.1 Single-phase uncontrolled converter circuits                                                                                                                                                                                                                               | 265       |

| 10         | 5.5.2 Active recovery 224                                                                                                                                                                                                                                                                           | 11.1.1 Half-wave circuit with an R-L load 265<br>11.1.1i - Equal area criterion<br>11.1.1ii - Load current zero slope criterion                                                                                                                                                 |           |

| Serie      | es and Parallel Device Operation                                                                                                                                                                                                                                                                    | 227 11.1.2 Half-wave circuit with an R-L load and freewheel Example 11.1: Half wave rectifier 11.1.3 Full-wave bridge circuit 271                                                                                                                                               | diode 268 |

| and        | Protection                                                                                                                                                                                                                                                                                          | 11.2 Single-phase full-wave half-controlled converter                                                                                                                                                                                                                           | 274       |

| 10.1       | Parallel and series operation of power devices 227  10.1.1 Series operation 227                                                                                                                                                                                                                     | 11.2i - Discontinuous load current 276 11.2ii - Continuous load current 276                                                                                                                                                                                                     |           |

|            | 10.1.1 Series operation 10.1.1i - Steady-state voltage sharing Example 10.1: Series device connection – static balancing 10.1.1ii - Transient voltage sharing                                                                                                                                       | 11.3 Single-phase controlled thyristor converter circuits                                                                                                                                                                                                                       | 277       |

264

| 741   | FOWER LIECTIONICS                                                                 |          |            |

|-------|-----------------------------------------------------------------------------------|----------|------------|

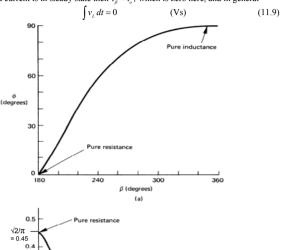

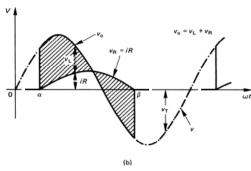

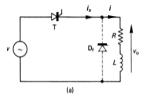

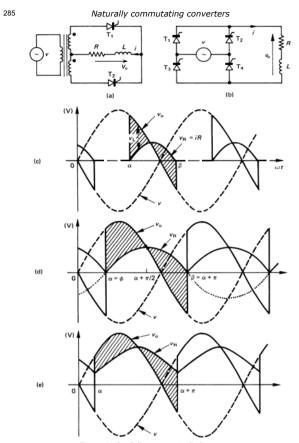

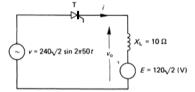

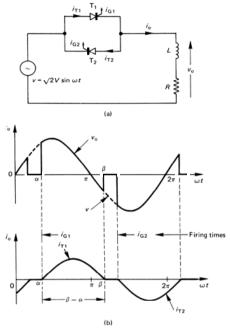

|       | 11.3.1 Half-wave circuit with an R-L load                                         | 277      |            |

|       | 11.3.1i - Case 1: Purely resistive load                                           |          |            |

|       | 11.3.1ii - Case 2: Purely inductive load                                          |          |            |

|       | Example 11.2: Half-wave controlled rectifier                                      |          |            |

|       | 11.3.2 Half-wave half-controlled                                                  | 282      |            |

|       | 11.3.2i - For discontinuous conduction                                            |          |            |

|       | 11.3.2ii - For continuous conduction                                              |          |            |

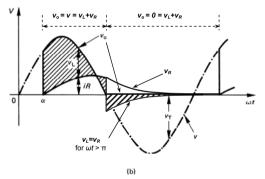

|       | 11.3.3 Full-wave circuit with an R-L load                                         | 286      |            |

|       | 11.3.3 $i$ - $\alpha > \phi$ , $\beta$ - $\alpha < \pi$ , discontinuous loa       | d curren | ıt         |

|       | 11.3.3ii - $\alpha = \phi$ , $\beta$ - $\alpha = \pi$ , verge of continuo         | ous load | current    |

|       | 11.3.3iii - $\alpha > \phi$ , $\beta$ - $\pi = \alpha$ , continuous load cu       | rrent    |            |

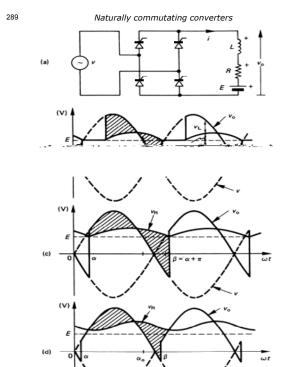

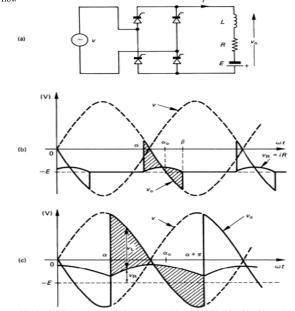

|       | 11.3.4 Full-wave circuit with R-L and emf load                                    | 288      |            |

|       | 11.3.4i - Discontinuous load current                                              |          |            |

|       | 11.3.4ii - Continuous load current                                                |          |            |

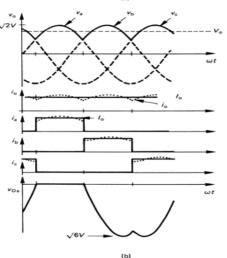

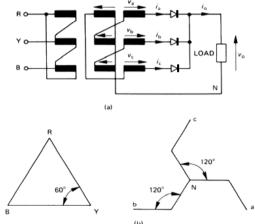

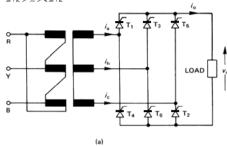

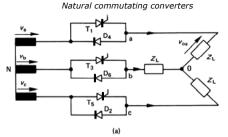

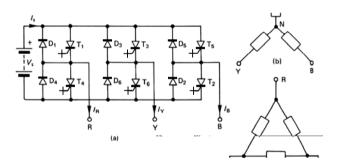

| 11.4  | Three-phase uncontrolled converter circuits                                       |          | 292        |

|       | 11.4.1 Half-wave rectifier circuit with an inductiv                               | e load 2 | 292        |

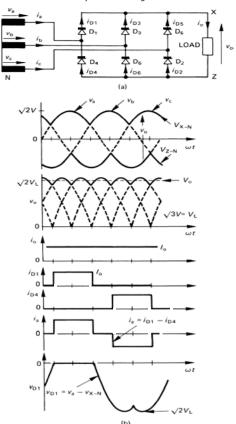

|       | 11.4.2 Full-wave rectifier circuit with an inductiv                               | e load 2 | 96         |

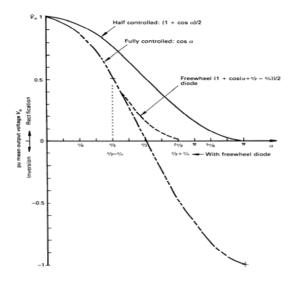

| 11.5  | 771 1 1 16 ( 11 1                                                                 |          | 207        |

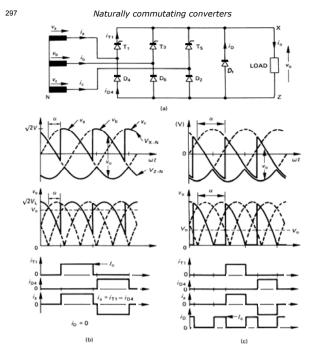

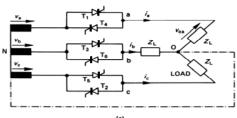

| 11.5  | Three-phase half-controlled converter                                             |          | 296        |

|       | 11.5i - For $\alpha \leq \frac{1}{3}\pi$                                          | 297      |            |

|       | 11.5ii - For $\alpha \geq \frac{1}{3}\pi$                                         | 298      |            |

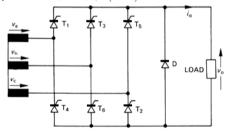

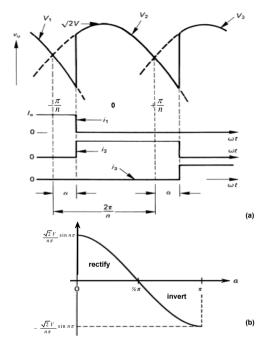

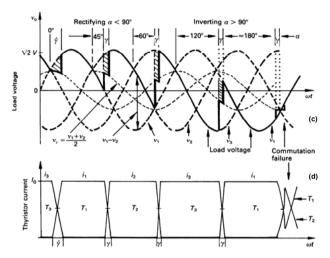

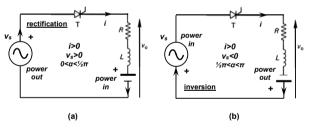

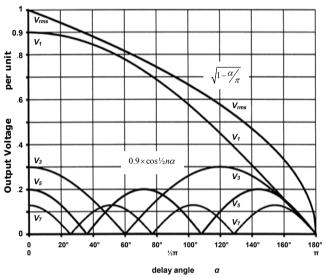

| 11.6  | Three-phase controlled thyristor converter circuit                                | ts       | 198        |

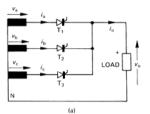

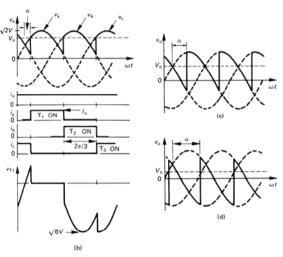

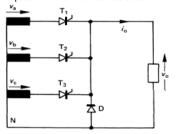

|       | 11.6.1 Half-wave circuit with an inductive load                                   | 298      |            |

|       | 11.6.2 Half-wave converter with freewheel diode                                   |          |            |

|       | 11.6.2 Italy-wave converter with freewheet alone $11.6.2i$ - For $\alpha < \pi/6$ | 300      |            |

|       | 11.6.2ii - For $\alpha > \pi/6$                                                   |          |            |

|       | 11.6.2iii - For α>5π/6                                                            |          |            |

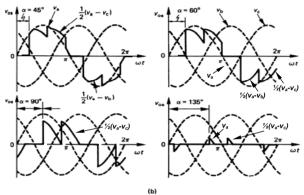

|       | 11.6.3 Full-wave circuit with an inductive load                                   | 301      |            |

|       | 11.6.4 Full-wave converter with freewheel diode                                   | 301      |            |

|       | Example 11.3: Converter average load voltage                                      |          |            |

|       | g                                                                                 |          |            |

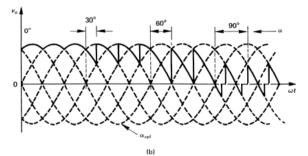

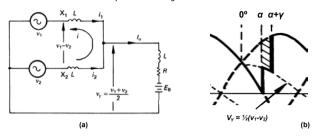

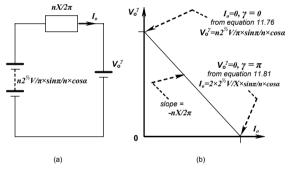

| 11.7  | Overlap                                                                           |          | 306        |

|       |                                                                                   |          |            |

| 11.8  | Overlap – inversion                                                               |          | 310        |

|       | E 1414 C                                                                          |          |            |

|       | Example 11.4: Converter overlap                                                   |          |            |

| 11.9  | Summary                                                                           |          | 312        |

|       | (i) Half-wave and full-wave, fully-controlled converter                           |          |            |

|       | (ii) Full-wave, half-controlled converter                                         |          |            |

|       | (ii) Half-wave and full-wave controlled converter with lo                         | ad fuare | haal diads |

|       | (iii) rauj-wave ana juu-wave controllea converter with lo                         | ua jreew | neet atode |

| 11.10 | Definitions                                                                       |          | 314        |

|       |                                                                                   |          |            |

| 12   |                                                                                                                                                                                                                    |            |     | 221 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-----|

| AC V | Voltage Regulators                                                                                                                                                                                                 |            |     | 321 |

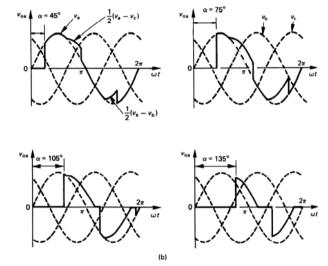

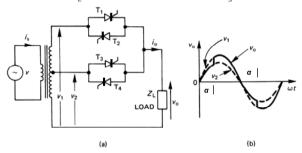

| 12.1 | Single-phase ac regulator 12.1i - Case 1: $\alpha > \phi$ 12.1ii - Case 2: $\alpha \leq \phi$                                                                                                                      |            | 321 |     |

|      | 12.1.1 Resistive Load Example 12.1a: single-phase ac regulator - 1 Example 12.1b: ac regulator - 2                                                                                                                 | 324        |     |     |

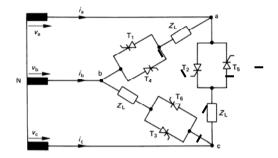

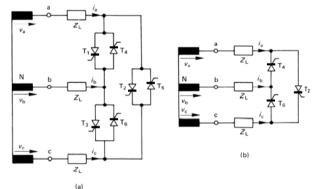

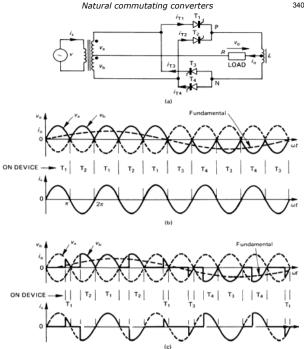

| 12.2 | Three-phase ac regulator                                                                                                                                                                                           |            | 328 |     |

|      | 12.2.1 Fully-controlled three-phase ac regulator i. $0 \le \omega t \le /\pi \pmod{2/3}$ ii. $\frac{1}{2} \pi \le \omega t \le /\pi \pmod{2/2}$ iii. $\frac{1}{2} \pi \le \omega t \le \frac{1}{2} \pi \pmod{0/2}$ | 328        |     |     |

|      | Example 12.2: Three-phase ac regulator 12.2.2 Half-controlled three-phase ac regulator i. $0 \le \alpha \le \%\pi$ ii. $\%\pi \le \alpha \le \%\pi$ iii. $\%\pi \le \alpha \le 7\pi/6$                             | 330        |     |     |

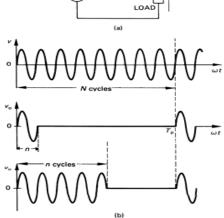

| 12.3 | Integral cycle control                                                                                                                                                                                             |            | 333 |     |

|      | Example 12.3: Integral cycle control                                                                                                                                                                               |            |     |     |

| 12.4 | Single-phase transformer tap-changer                                                                                                                                                                               |            | 337 |     |

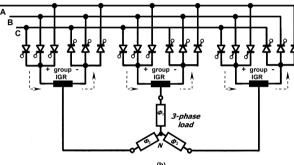

| 12.5 | Cycloconverter                                                                                                                                                                                                     |            | 338 |     |

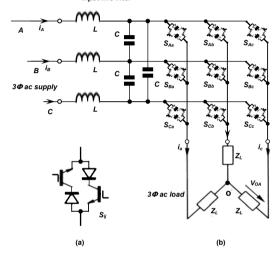

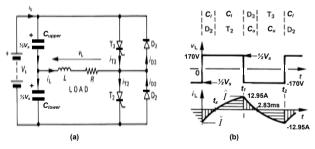

| 12.6 | The matrix converter                                                                                                                                                                                               |            | 341 |     |

| 12.7 | Load efficiency and supply current power factor                                                                                                                                                                    |            | 343 |     |

|      | 12.7.1 Load waveforms 12.7.2 Supply waveforms Example 12.4: Load efficiency                                                                                                                                        | 343<br>344 |     |     |

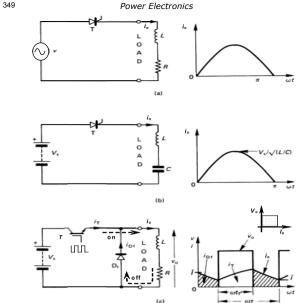

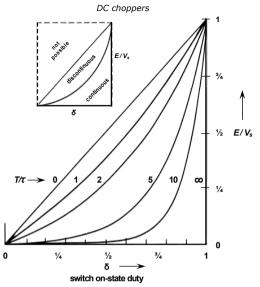

| 13   |                                                                                                                                                                                                                    |            |     | 348 |

| DC ( | Choppers                                                                                                                                                                                                           |            |     | 348 |

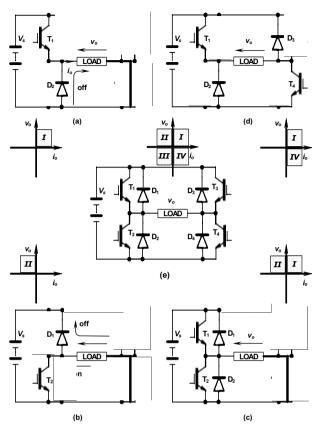

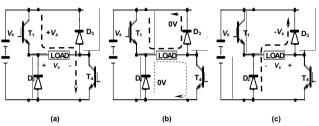

| 13.1 | DC chopper variations                                                                                                                                                                                              |            | 348 |     |

13.3

13.4

13.5

13.6

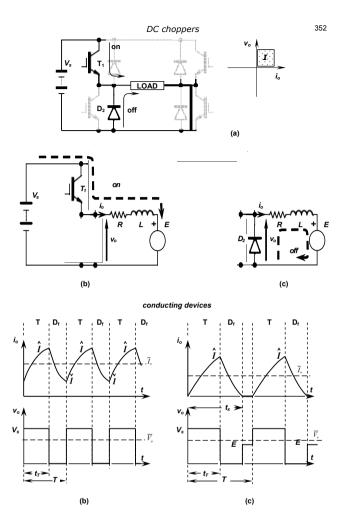

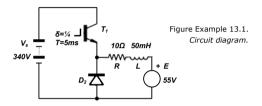

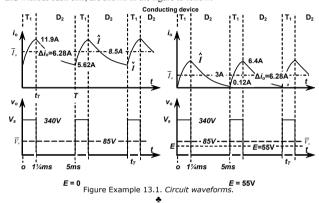

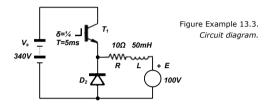

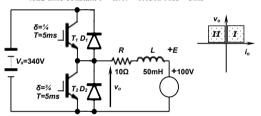

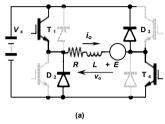

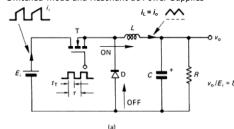

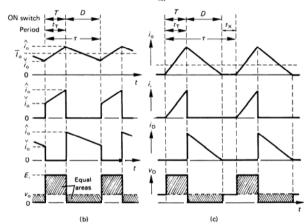

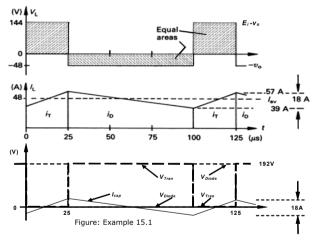

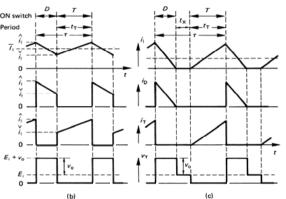

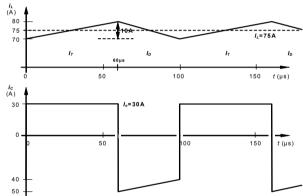

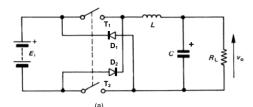

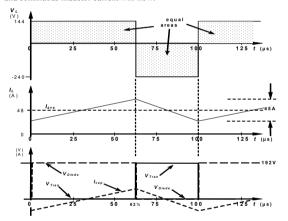

13.2 First Quadrant dc chopper

351

412

Power Electronics

14

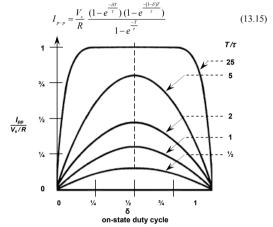

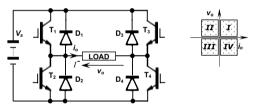

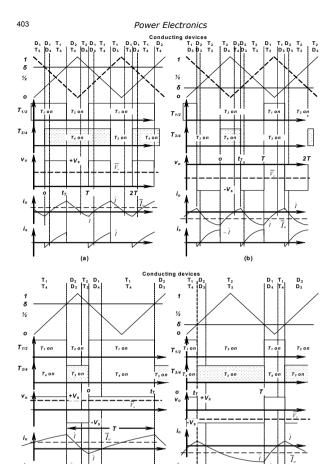

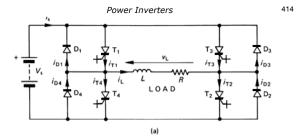

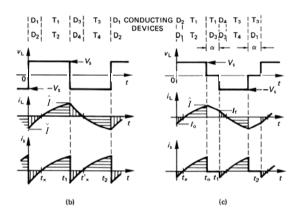

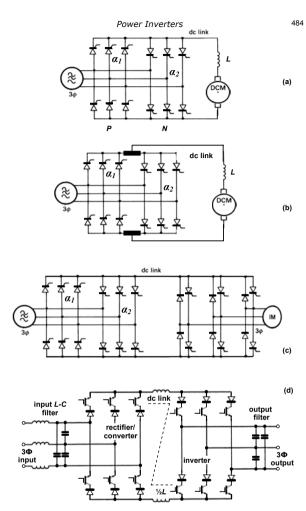

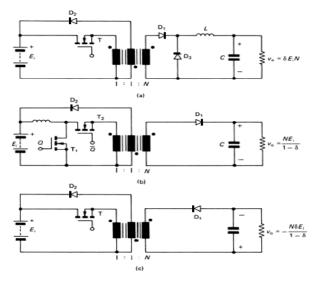

| 13.2.1 Continuous load current  353  Steady-state time domain analysis of first quadrant chopper                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Power Inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

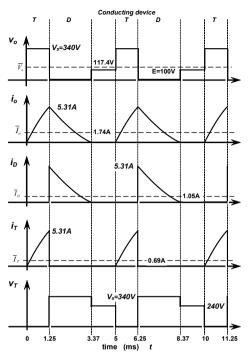

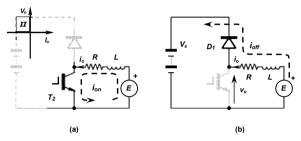

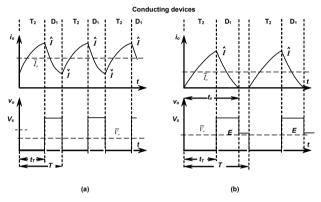

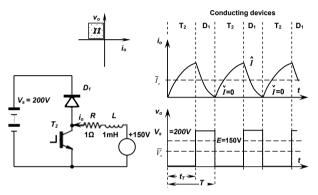

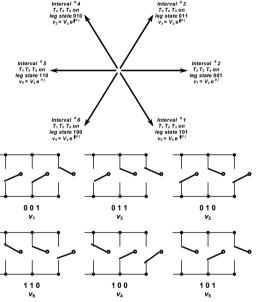

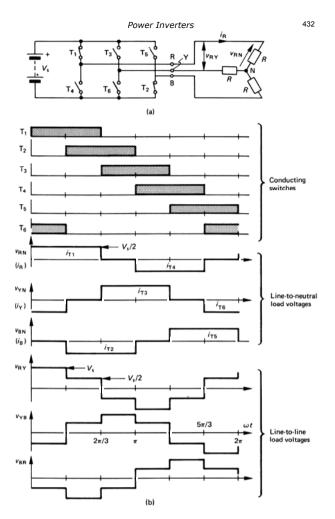

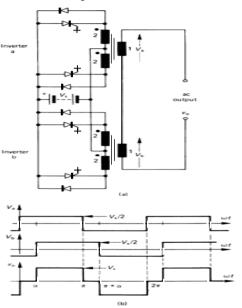

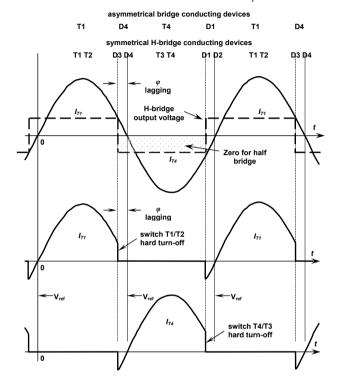

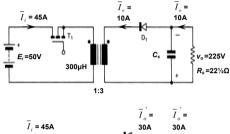

| - with load back emf and continuous output current i. Fourier coefficients ii. Time domain differential equations  13.2.2 Discontinuous load current  Steady-state time domain analysis of first quadrant chopper - with load back emf and discontinuous output current i. Fourier coefficients ii. Time domain differential equations  Example 13.1: DC chopper with load back emf (first quadrant)  Example 13.2: DC chopper with load back emf - verge of discontinuous conduction  Example 13.3: DC chopper with load back emf - discontinuous conduction | 14.1 dc to ac voltage-fed inverter bridge topologies  14.1.1 Single-phase voltage-fed inverter bridge 413 i Square-wave output ii Quasi-square-wave output Example 14.1a: Single-phase H-bridge with an L-R load Example 14.1b: H-bridge inverter ac output factors Example 14.2: Harmonic analysis of H-bridge with an L-R load Example 14.3: Single-phase half-bridge with an L-R load  14.1.2 Three-phase voltage-fed inverter bridge 424 i 180° (π) conduction ii 120° (%π) conduction |

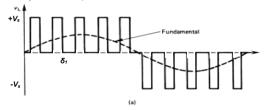

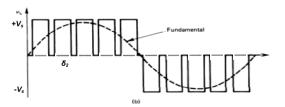

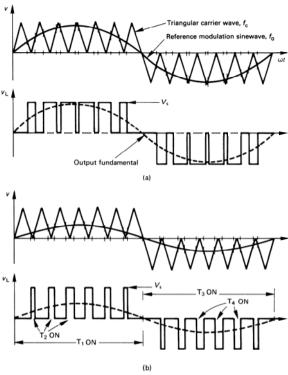

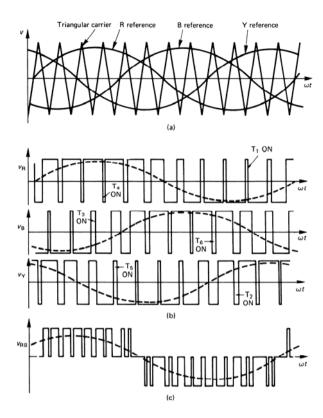

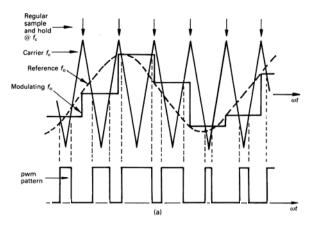

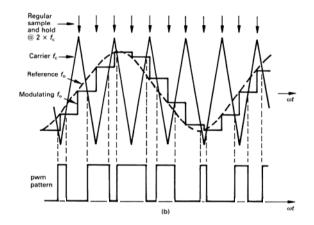

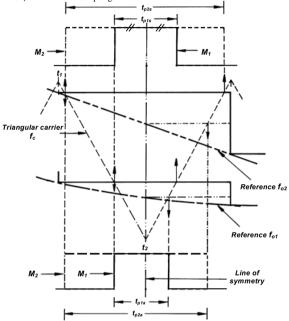

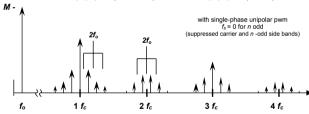

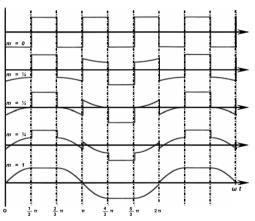

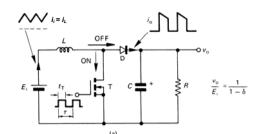

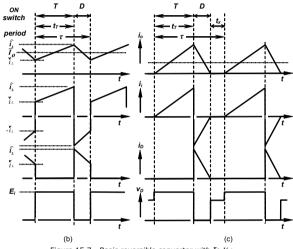

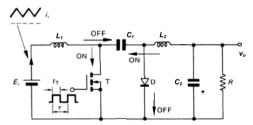

| Second Quadrant dc chopper 371  13.3.1 Continuous inductor current 372  13.3.2 Discontinuous inductor current 375  Example 13.4: Second quadrant DC chopper - continuous conduction                                                                                                                                                                                                                                                                                                                                                                           | 14.1.3 Inverter output voltage and frequency control techniques 431 14.1.3i - Variable voltage dc link 14.1.3ii - Single-pulse width modulation 14.1.3iii - Multi-pulse width modulation 14.1.3iv - Multi-pulse, selected notching modulation                                                                                                                                                                                                                                              |

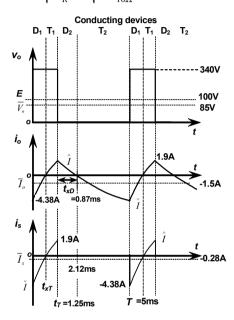

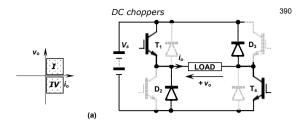

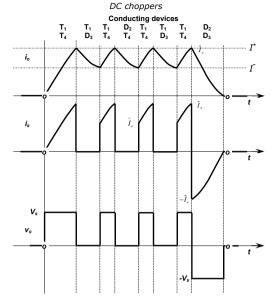

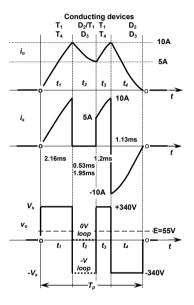

| Two quadrant dc chopper - Q I and QII 380  i. $\check{I} > 0$ , $\hat{I} > 0$ and $\overline{I}_o > 0$ ii. $\check{I} < 0$ , $\hat{I} > 0$ and $\overline{I}_o > 0$ iii. $\check{I} < 0$ , $\hat{I} > 0$ and $\overline{I}_o < 0$ iv. $\check{I} < 0$ , $\hat{I} < 0$ and $\overline{I}_o < 0$ Example 13.5: Two quadrant DC chopper with load back emf                                                                                                                                                                                                       | 14.1.3v - Sinusoidal pulse-width modulation (pwm)<br>1 - Natural sampling<br>(a) Synchronous carrier<br>(b) Asynchronous carrier<br>2 - Regular sampling<br>(a) Asynchronous carrier<br>Symmetrical modulation                                                                                                                                                                                                                                                                             |

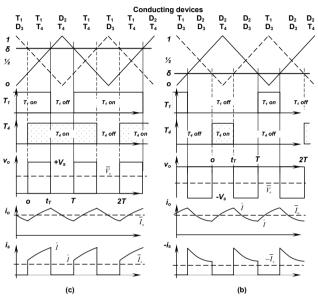

| Two quadrant dc chopper – Q 1 and Q IV  State #1 State #2 State #3  13.5.1 dc chopper: – Q I and Q IV – multilevel output voltage switching 392  13.5.2 dc chopper: – Q I and Q IV – bipolar voltage switching 393                                                                                                                                                                                                                                                                                                                                            | Asymmetrical modulation 3 - Frequency spectra of pwm waveforms 14.1.3vi - Phase dead-banding 14.1.3vii - Triplen Injection modulation                                                                                                                                                                                                                                                                                                                                                      |

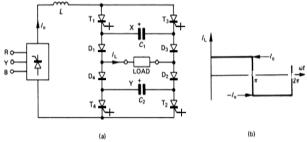

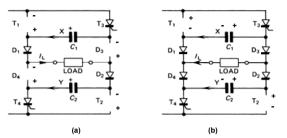

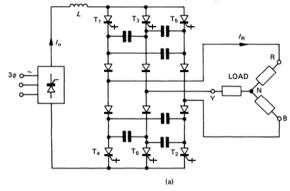

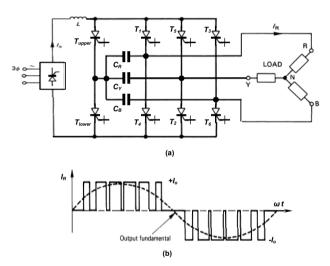

| 13.5.3 Multilevel output voltage states, dc chopper 395 Example 13.6: Asymmetrical, half H-bridge, dc chopper Four quadrant dc chopper 400                                                                                                                                                                                                                                                                                                                                                                                                                    | 14.2.1 Single-phase current fed inverter 450 14.2.2 Three-phase current fed inverter 451                                                                                                                                                                                                                                                                                                                                                                                                   |

| 13.6.1 Unified four quadrant dc chopper - bipolar voltage output switching 401 13.6.2 Unified four quadrant dc chopper - multilevel voltage output switching 405 Example 13.7: Four quadrant dc chopper                                                                                                                                                                                                                                                                                                                                                       | 14.3 Resonant inverters 455  14.3.1 L-C resonant circuits 456  14.3.1i - Series resonant L-C-R circuit  14.3.1ii - Parallel resonant L-C-R circuit                                                                                                                                                                                                                                                                                                                                         |

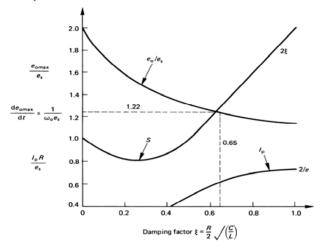

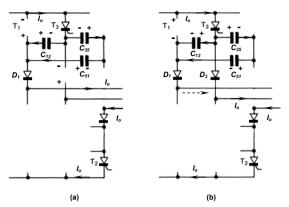

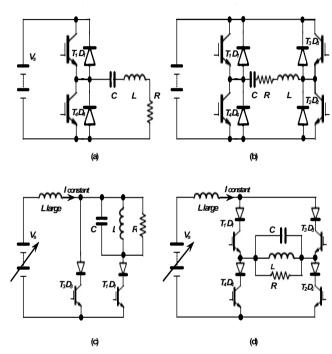

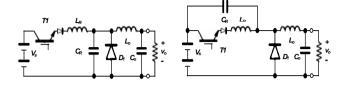

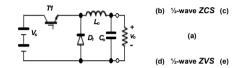

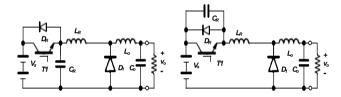

|      | 14.3.2  | Series resonant inverters  14.3.2i - Series resonant inverter – single 1 - Lagging operation (advancing the content of the con | ne switch | turn-off angle) |

|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|

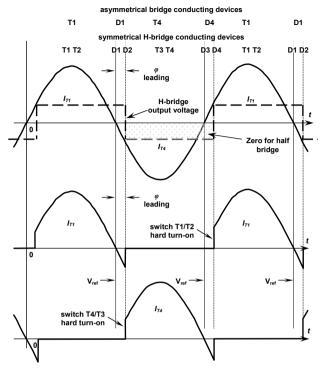

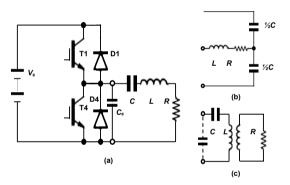

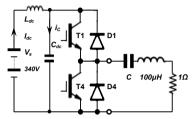

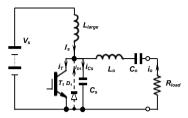

|      |         | 14.3.2ii - Series resonant inverter - H-b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | verter    |                 |

|      |         | 14.3.2iii - Circuit variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                 |

|      | 14.3.3  | Parallel resonant inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 465       | 4               |

|      |         | 14.3.3i - Parallel resonant inverter – sing<br>14.3.3ii - Parallel resonant inverter – H-l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           | 0               |

|      |         | Example 14.4: Half-bridge with a serie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                 |

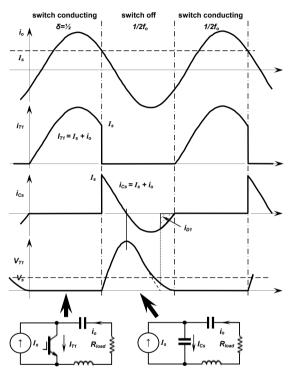

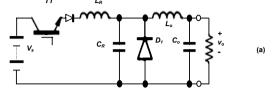

|      | 14.3.4  | Single-switch current source series reson                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                 |

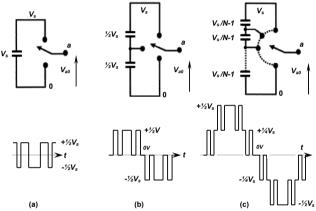

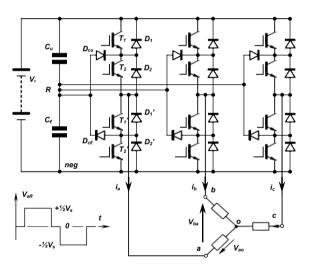

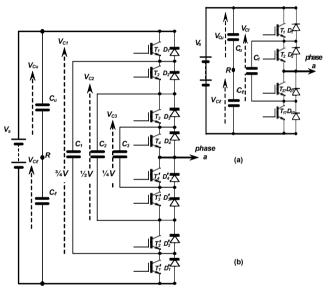

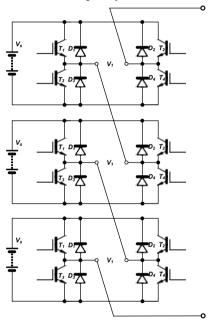

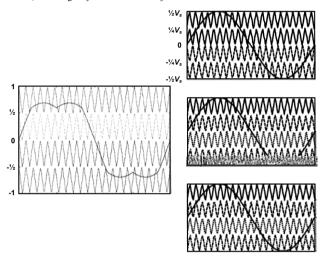

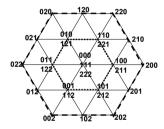

| 14.4 | Multi-l | evel voltage-source inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | 472             |